PCIe 7.0 to Reach 512 GB/s, Arriving in 2025

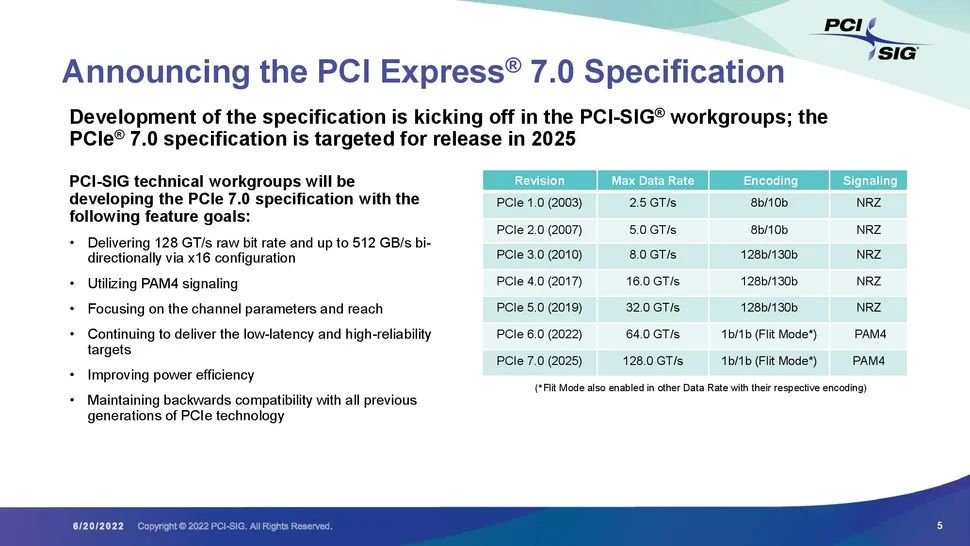

The PCI-SIG Developers Conference 2022 is in full swing, and today the standards committee behind the ubiquitous PCIe interface announced that the PCIe 7.0 specification is targeted for release to its members in 2025 with a data rate up to 128 GT/s. That equates to 512 GB/s of bi-directional throughput via a 16-lane (x16) connection, before encoding overhead. As a reminder, the PCI-SIG is the consortium behind the PCIe interface, an open industry standard comprised of over 900 member companies.

The PCI-SIG notes that the PCIe 7.0 interface will provide a blistering 512 GB/s of bi-directional throughput over a x16 connection, but that is before encoding overhead and the impact of header efficiency, both of which affect the usable bandwidth.

The PCIe 7.0 interface will continue to use 1b/1b flit mode encoding and the PAM4 signaling tech introduced with PCIe 6.0, a notable improvement over the 128b/130b encoding and NRZ signaling used with the 3.0 to 5.0 specifications. As such, the real-world usable bandwidth will be somewhat lower than the 512 GB/s figure but still represent a doubling over the PCIe 6.0 interface.

As we saw with the jump to PCIe 4.0 and 5.0, the length of PCIe traces will again shorten due to the faster signaling rates. This means the minimum allowable distance without additional componentry between the PCIe root device, like a CPU, and the end device, like a GPU, will shorten. As a result, motherboards will need more retimers and thicker PCBs comprised of higher-quality materials than we saw with prior generations of the interface. This means that PCIe 7.0 support will result in yet another hike in motherboard pricing.

Notably, the higher bandwidth per lane, now at 32 GB/s bi-directional for a x1 connection, could allow for 'thinner' connections for some devices (like using a x4 instead of a x8 connection, for instance).

The groundwork for the PCIe 7.0 specification comes after PCI-SIG finalized the PCIe 6.0 specification earlier this year. PCIe 6.0 devices began coming to market in April from Renesas. However, it will still be some time before we see devices like SSDs and GPUs that support this speedy interface — these specifications are typically ratified and finalized long before we see shipping silicon.

As you'll notice, there still aren't many PCIe 5.0 devices on the market yet, either, though the interface did come to mainstream motherboards with Intel's Alder Lake and will also make an appearance on AMD's upcoming Zen 4 Ryzen 7000 platform that arrives later this year. The first PCIe 5.0 SSDs will arrive at the same time as the Ryzen 7000 processors, but we've already seen product announcements for PCIe 5.0 devices for data centers and AI/ML gear.

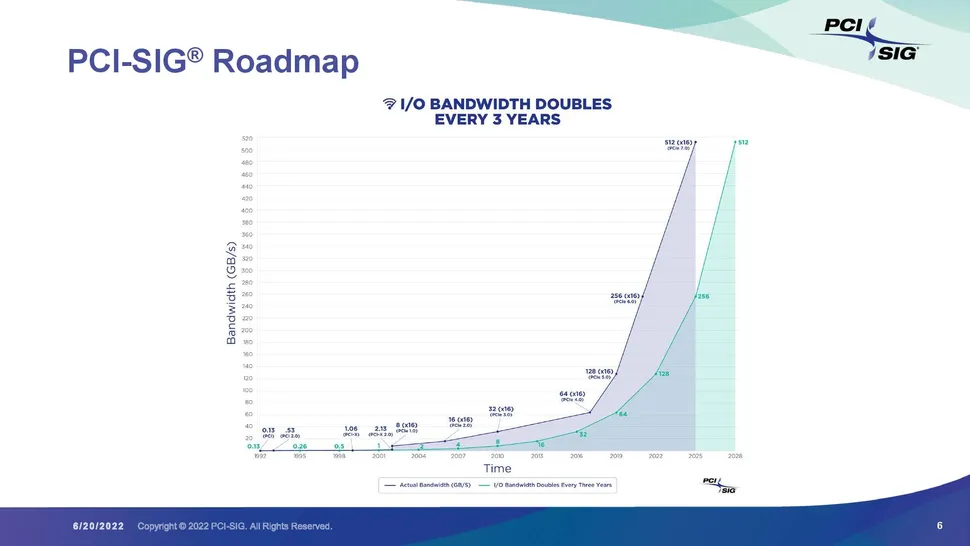

In other words, you won't see PCIe 7.0 devices on the market for quite some time, though the PCI-SIG is starting to define the specification now and hopes to meet its goal of delivering a new spec every three years. The PCIe 7.0 spec is expected to land in 2025, but we won't see end devices until about 18 months after the spec is finalized.

- PCIe 7.0 Specification Goals:

- Delivering 128 GT/s raw bit rate and up to 512 GB/s bi-directionally via x16 configuration

- Utilizing PAM4 (Pulse Amplitude Modulation with 4 levels) signaling

- Focusing on the channel parameters and reach

- Continuing to deliver low-latency and high-reliability targets

- Improving power efficiency

- Maintaining backwards compatibility with all previous generations of PCIe technology

The PCI-SIG hasn't shared many of the details of the interface yet, but we're sure to learn more as it works its way through the definition phase. In the meantime, here's the full press deck for your perusal.