Pcie controller mode change

Mar 04, 2024

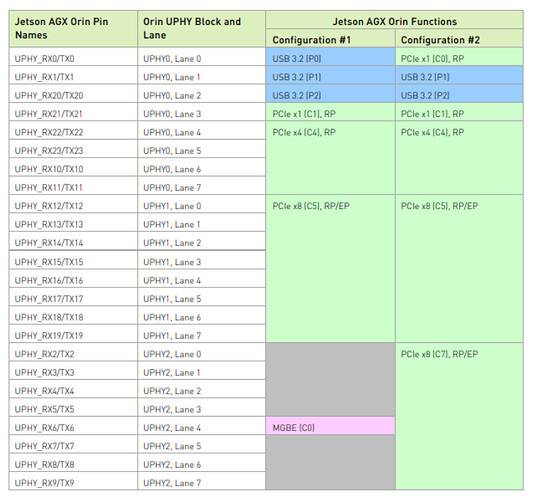

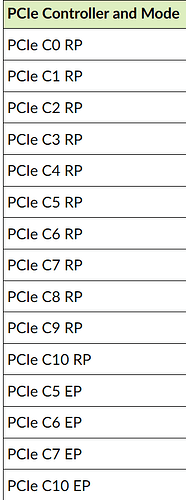

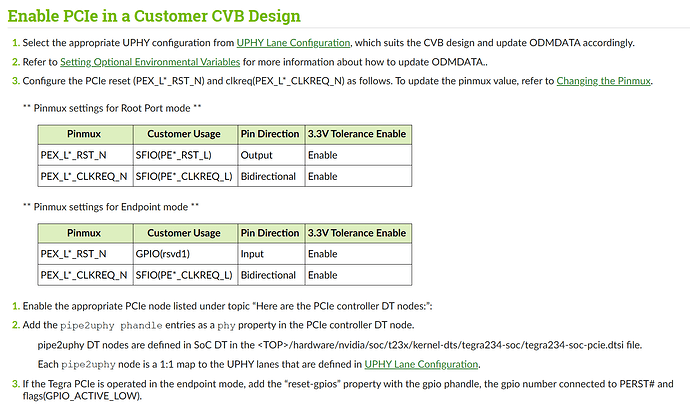

Question 1: Jetson AGX Orin (Root point) and FPGA VCU 118 (end point), communicating through a pcie device, how to set Jetson’s controller mode to the desired CX (X: 0~10):

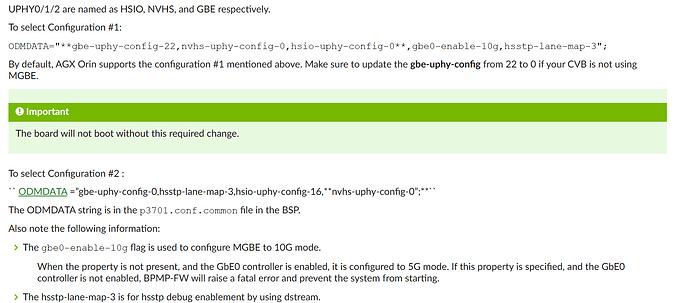

is to make changes to ODMDATA:

Still using this approach:

Is there a difference between these two ways? Which one is easier?

Question 2: Also is there any more detailed documentation explaining about this UPHY Lane Configuration?