Using Xavier NX as PCIe root complex for AGX Orin endpoint

Mar 04, 2024

Hello,

Can anyone give advice on bringing up a Xavier NX M.2 <–> AGX Orin PCIe x16 connection? I’ve been stuck on this for several days, after numerous debug steps (both software + hardware).

Background:

- I am trying to validate AGX Orin PCIe Endpoint with a Xavier NX Root. We only have one x16 device (a single Orin AGX), so the Root port is a Xavier NX’s M.2 NVMe slot.

- Both devices are running Jetpack 5.1.1, r35.3.1.

- We have a custom PCIe swap board designed with NVIDIA’s PCIe Endpoint Design Guidelines.

- I’ve gone through the PCIe Endpoint Mode steps, up through reading/writing the Endpoint RAM via

busybox devmemcommands on the AGX Orin side, but the two Jetsons still don’t detect/enumerate each other withlspci -v. - I made a previous post in the AGX Orin forums, but was unable to resolve this issue.

My thinking: Could there be some special kernel config or patch on the Xavier NX side that I’m unaware of, since M.2 (RP) supports only upto x4 while the physical AGX Orin slot is x16?

Physical setup:

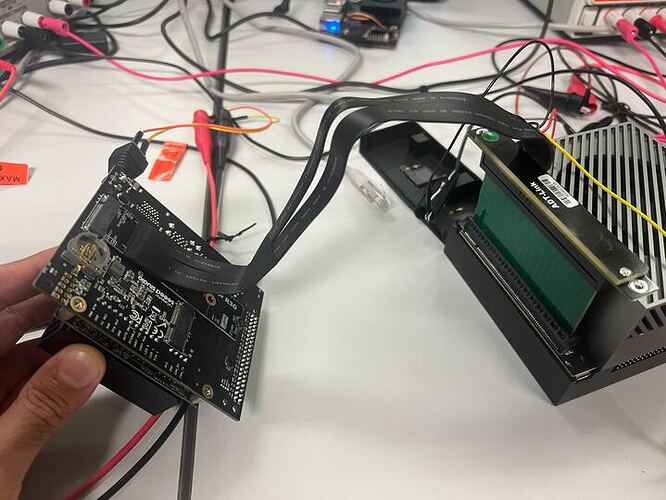

- Photo of setup is attached below.

- Xavier NX is Root (RP), Orin AGX is Endpoint (EP).

- We use an ADT-Link adapter for the M.2 NVMe-to-PCIe x16 connection, which was shown to work between 2 Jetsons in this old post.

- We have a custom TX/RX swap board designed using the PCIe Endpoint Design Guidelines application note.

Debug steps we have tried / verified:

- Replacing the Xavier NX RP with a different machine that has an M.2 slot (still did not detect AGX Orin EP). Sadly, I do not a second x16 device to test with, so using the adapter + M.2 x4 device is required…

- Custom PCIe swap board’s buffers are getting power correctly.

- Tracing connectivity between the M.2 side’s pins and AGX Orin’s PCIe pins (i.e. crossover is correct)

- Re-checking Endpoint’s custom kernel, ODMData, flash steps - all are fine.

- Different methods of powering the PCIe slot M.2 to x16 adapter (bench 12v supply vs wall adapter - I was concerned the slot was being powered incorrectly, but it has no effect .)

- Re-enumerating the PCIe bus using

echo 1 > /sys/bus/pci/rescanand changing the RP / EP boot order - no effect.

Can anyone with hardware experience on the Xavier NX’s PCIe side help us here?