AGX Xavier Single Node Nets

Hi Nvidia Forums!

I’m interested in designing a custom carrier board with an AGX Xavier. I also want to design it so that it is forward compatible with the AGX Orin. The purpose is specifically for PCIe, where there will be three 4-lane buses. My questions are as follows.

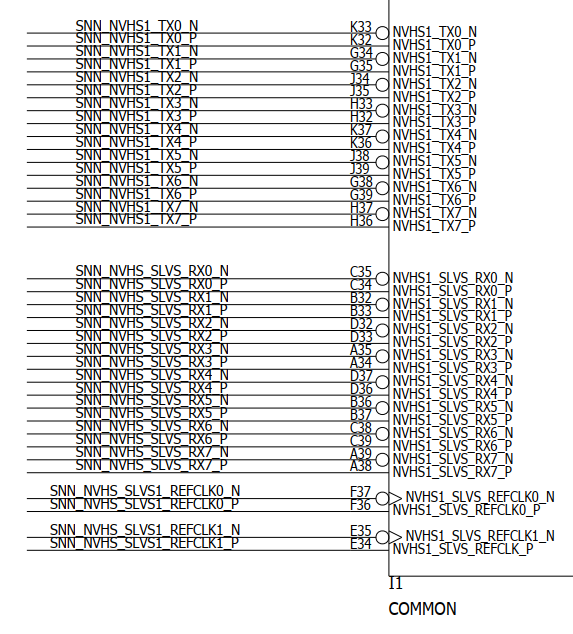

1. Single Node Network (SNN): Is it possible to use the AGX Xavier pins connected to the SNN nets for high-speed differential signals (PCIe), or are these pins just dead ends?

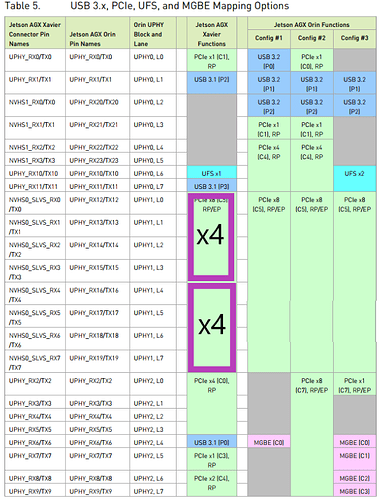

2. PCIe block partitioning: Is it possible to operate two separate x4 PCIe buses within a single x8 PCIE block? (e.g., via Pinmux and Device Tree customization)

3. AGX Orin USB 3.x, PCIe, UFS, and MGBE Mapping Options: Are the AGX Orin configurations limited to only the stated three options in the image above, or can they be further customized?

Thanks!

Ian