Jetson AGX Orin pcie clock config

Hi,

I’m having problems using and configuring the custom board.

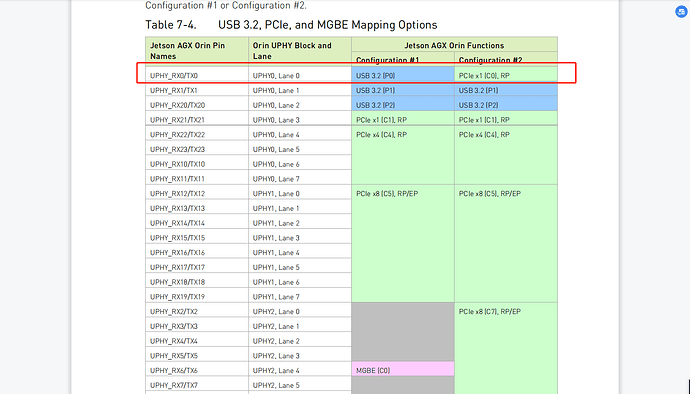

I used PCIe x1 in config2 mode as 1G PHY, and the PHY chip model was REALTEK RTL8111H.

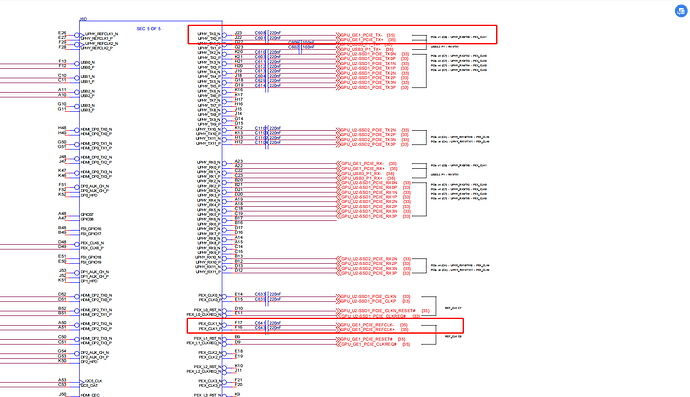

Here is a schematic of my custom board, which illustrates the pin references of orin.

Device tree node configuration:```

rtl8111h_phy: phy@1 {

compatible = “realtek,rtl8111h-cg”;

reg = ;

#phy-cells = ;

phy-mode = “rgmii”;

clock-in-out = “input”;

nvidia,reset-gpios = <&tegra_main_gpio TEGRA234_MAIN_GPIO(Q, 7) GPIO_ACTIVE_LOW>;

pcie@1,0 {

status = “okay”;

phy-names = “pcie-phy”;

phys = <&rtl8111h_phy>;

device_type = “pci”;

#address-cells =

;

#size-cells =

;

ranges;

bus-range = <0x00 0xff>;

reg = <0x0 0xc400000 0x0 0x4000000 0x0 0x20000000 0x0 0x80000000>;

num-lanes =

;

max-link-speed = ;

max-link-width =

;

interrupts = <0 IRQ_TYPE_LEVEL_HIGH 0>;

interrupt-names = “intr”;

};

};

dmesg | grep pci:```

root@nvidia-agx-orin:/sys/kernel/debug# dmesg | grep pci

[ 4.453161] ohci-pci: OHCI PCI platform driver

[ 7.400596] tegra194-pcie 14100000.pcie: Adding to iommu group 9

[ 7.413276] tegra194-pcie 14100000.pcie: Using GICv2m MSI allocator

[ 7.420456] tegra194-pcie 14160000.pcie: Adding to iommu group 10

[ 7.433088] tegra194-pcie 14160000.pcie: Using GICv2m MSI allocator

[ 7.439986] tegra194-pcie 141a0000.pcie: Adding to iommu group 11

[ 7.451950] tegra194-pcie 141a0000.pcie: Using GICv2m MSI allocator

[ 7.458443] tegra194-pcie 141a0000.pcie: Failed to get slot regulators: -517

[ 9.741472] tegra194-pcie 14100000.pcie: Using GICv2m MSI allocator

[ 9.752588] tegra194-pcie 14100000.pcie: host bridge /pcie@14100000 ranges:

[ 9.764470] tegra194-pcie 14100000.pcie: IO 0x0030100000..0x00301fffff -> 0x0030100000

[ 9.773172] tegra194-pcie 14100000.pcie: MEM 0x20a8000000..0x20afffffff -> 0x0040000000

[ 9.785565] tegra194-pcie 14100000.pcie: MEM 0x2080000000..0x20a7ffffff -> 0x2080000000

[ 10.905169] tegra194-pcie 14100000.pcie: Phy link never came up

[ 10.911341] tegra194-pcie 14100000.pcie: PCI host bridge to bus 0001:00

[ 10.918158] pci_bus 0001:00: root bus resource [bus 00-ff]

[ 10.923793] pci_bus 0001:00: root bus resource [io 0x0000-0xfffff] (bus address [0x30100000-0x301fffff])

[ 10.933628] pci_bus 0001:00: root bus resource [mem 0x20a8000000-0x20afffffff] (bus address [0x40000000-0x47ffffff])

[ 10.944440] pci_bus 0001:00: root bus resource [mem 0x2080000000-0x20a7ffffff pref]

[ 10.952370] pci 0001:00:00.0: [10de:229e] type 01 class 0x060400

[ 10.958702] pci 0001:00:00.0: PME# supported from D0 D3hot

[ 10.972587] pci 0001:00:00.0: PCI bridge to [bus 01-ff]

[ 10.977989] pci 0001:00:00.0: Max Payload Size set to 256/ 256 (was 256), Max Read Rq 512

[ 10.986954] pcieport 0001:00:00.0: Adding to iommu group 9

[ 10.992872] pcieport 0001:00:00.0: PME: Signaling with IRQ 63

[ 10.999179] pcieport 0001:00:00.0: AER: enabled with IRQ 63

[ 11.005153] pci_bus 0001:01: busn_res: [bus 01-ff] is released

[ 11.011262] pci 0001:00:00.0: Removing from iommu group 9

[ 11.016821] pci_bus 0001:00: busn_res: [bus 00-ff] is released

[ 11.024589] tegra194-pcie 14160000.pcie: Using GICv2m MSI allocator

[ 11.032221] tegra194-pcie 14160000.pcie: host bridge /pcie@14160000 ranges:

[ 11.039397] tegra194-pcie 14160000.pcie: IO 0x0036100000..0x00361fffff -> 0x0036100000

[ 11.048091] tegra194-pcie 14160000.pcie: MEM 0x2428000000..0x242fffffff -> 0x0040000000

[ 11.056767] tegra194-pcie 14160000.pcie: MEM 0x2140000000..0x2427ffffff -> 0x2140000000

[ 12.173312] tegra194-pcie 14160000.pcie: Phy link never came up

[ 12.179465] tegra194-pcie 14160000.pcie: PCI host bridge to bus 0004:00

[ 12.186281] pci_bus 0004:00: root bus resource [bus 00-ff]

[ 12.191919] pci_bus 0004:00: root bus resource [io 0x100000-0x1fffff] (bus address [0x36100000-0x361fffff])

[ 12.202014] pci_bus 0004:00: root bus resource [mem 0x2428000000-0x242fffffff] (bus address [0x40000000-0x47ffffff])

[ 12.212839] pci_bus 0004:00: root bus resource [mem 0x2140000000-0x2427ffffff pref]

[ 12.220758] pci 0004:00:00.0: [10de:229c] type 01 class 0x060400

[ 12.227096] pci 0004:00:00.0: PME# supported from D0 D3hot

[ 12.240763] pci 0004:00:00.0: PCI bridge to [bus 01-ff]

[ 12.246157] pci 0004:00:00.0: Max Payload Size set to 256/ 256 (was 256), Max Read Rq 512

[ 12.255109] pcieport 0004:00:00.0: Adding to iommu group 10

[ 12.261080] pcieport 0004:00:00.0: PME: Signaling with IRQ 65

[ 12.267389] pcieport 0004:00:00.0: AER: enabled with IRQ 65

[ 12.273358] pci_bus 0004:01: busn_res: [bus 01-ff] is released

[ 12.279441] pci 0004:00:00.0: Removing from iommu group 10

[ 12.285090] pci_bus 0004:00: busn_res: [bus 00-ff] is released

[ 12.292672] tegra194-pcie 141a0000.pcie: Using GICv2m MSI allocator

[ 12.299134] tegra194-pcie 141a0000.pcie: Failed to get slot regulators: -517

[ 12.299232] vdd-3v3-pcie: supplied by vdd-3v3-sys

[ 12.355790] tegra194-pcie 141a0000.pcie: Using GICv2m MSI allocator

[ 12.468895] tegra194-pcie 141a0000.pcie: host bridge /pcie@141a0000 ranges:

[ 12.476077] tegra194-pcie 141a0000.pcie: IO 0x003a100000..0x003a1fffff -> 0x003a100000

[ 12.484760] tegra194-pcie 141a0000.pcie: MEM 0x2b28000000..0x2b2fffffff -> 0x0040000000

[ 12.493445] tegra194-pcie 141a0000.pcie: MEM 0x2740000000..0x2b27ffffff -> 0x2740000000

[ 13.608893] tegra194-pcie 141a0000.pcie: Phy link never came up

[ 13.615044] tegra194-pcie 141a0000.pcie: PCI host bridge to bus 0005:00

[ 13.621866] pci_bus 0005:00: root bus resource [bus 00-ff]

[ 13.627502] pci_bus 0005:00: root bus resource [io 0x200000-0x2fffff] (bus address [0x3a100000-0x3a1fffff])

[ 13.637617] pci_bus 0005:00: root bus resource [mem 0x2b28000000-0x2b2fffffff] (bus address [0x40000000-0x47ffffff])

[ 13.648441] pci_bus 0005:00: root bus resource [mem 0x2740000000-0x2b27ffffff pref]

[ 13.656355] pci 0005:00:00.0: [10de:229a] type 01 class 0x060400

[ 13.662686] pci 0005:00:00.0: PME# supported from D0 D3hot

[ 13.676464] pci 0005:00:00.0: PCI bridge to [bus 01-ff]

[ 13.681864] pci 0005:00:00.0: Max Payload Size set to 256/ 256 (was 256), Max Read Rq 512

[ 13.690808] pcieport 0005:00:00.0: Adding to iommu group 11

[ 13.696795] pcieport 0005:00:00.0: PME: Signaling with IRQ 67

[ 13.702955] pcieport 0005:00:00.0: AER: enabled with IRQ 67

[ 13.708925] pci_bus 0005:01: busn_res: [bus 01-ff] is released

[ 13.715001] pci 0005:00:00.0: Removing from iommu group 11

[ 13.720646] pci_bus 0005:00: busn_res: [bus 00-ff] is released

Now the question:

1.PEX_CLK0_N and PEX_CLK0_P have no clock signal output, which may cause that pci 1G PHY cannot be recognized in the system.I used the oscilloscope to look at the pins and found no clock output.